A Londres, HPE dévoile les dessous de The Machine

La mémoire persistante est la clé des architectures informatiques du futur, estime HPE. A Discover Londres, la firme a dévoilé les éléments centraux de son prototype d'architecture "Memory Driven" et levé le voile sur sa stratégie en matière de stockage mémoire.

À l’occasion de sa conférence annuelle Discover Europe 2016, qui s’est tenue à Londres, HPE a montré les premiers composant du prototype fonctionnel issu de son programme de recherche « The Machine » visant à développer une nouvelle architecture informatique à base de mémoire persistante.

Depuis l’Edvac, le coût de la mémoire a toujours été le principal obstacle à la performance des architectures de type von Neumann. « Idéalement », expliquait von Neuman en 1946, « notre désir serait de disposer d’une quantité infinie de mémoire [de telle sorte que chaque mot soit disponible en mémoire]. Il ne semble pas possible d’atteindre cet objectif. Nous sommes donc contraints de nous appuyer sur une hiérarchie de mémoires, toutes plus capacitives que les précédentes, mais aussi plus lentes ».

C’est ainsi que dans un ordinateur, on a vu émerger une hiérarchie sans cesse croissante de couche de stockage de données, de la mémoire cache du processeur (niveau un, niveau deux, niveau trois) à la mémoire vive (DRAM) - pour le stockage adressable en mode page, en passant par les SSD ou les disques durs — pour le stockage adressable en mode bloc, ou la bande.

L'émergence d'architectures conçues pour la mémoire persistante

L’émergence récente de nouveaux supports, tels que la 3D Xpoint d’Intel, ou tels que la mémoire ReRAM chez SanDisk (attendue à l’horizon 2018/2019), ouvre la voie à un rapprochement entre mémoire et stockage. Ces nouveaux supports persistants ont en effet des performances plus proches de la mémoire vive que de celle des disques durs. Et ils sont adressables en mode page.

Pour donner un nouveau souffle aux architectures IT, l’objectif d’HPE est de promouvoir l’émergence d’architectures basées à 100 % sur ces technologies mémoires. C’est ce qui a guidé les chercheurs d’HPE travaillant sur le programme « The Machine »

« The Machine est le programme de recherche le plus ambitieux jamais lancé par HPE. Les architectures historiques ont toutes été bâties autour des microprocesseurs. The Machine met en avant les données, avant le processeur. L’objectif est de permettre de les traiter en quasi temps-réel » explique Kirk Bresniker, le CTO de la division entreprises d’HPE lors d’une rencontre avec la presse à Londres, en marge du HPE Discover.

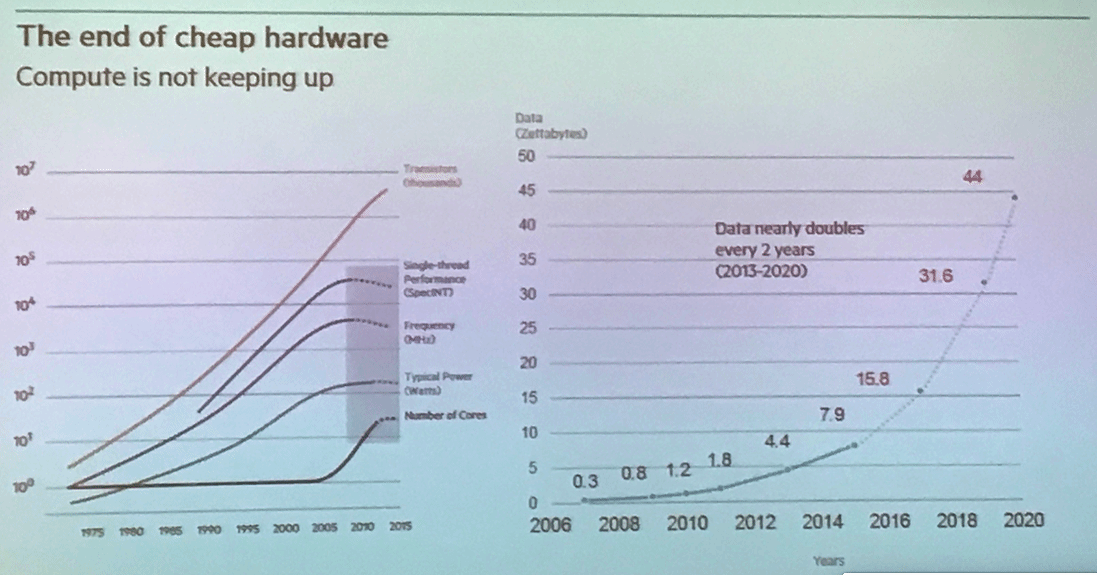

HPE estime que l'on approche les limites de la loi de Moore et qu'il faut imaginer de nouvelles architectures pour doper les performances des systèmes informatiques afin de faire face à l'explosion des volumes de données.

HPE estime que l'on approche les limites de la loi de Moore et qu'il faut imaginer de nouvelles architectures pour doper les performances des systèmes informatiques afin de faire face à l'explosion des volumes de données.

Pointant du doigt les difficultés croissantes des fabricants à produire des puces dans des géométries de gravure de plus en plus fine, Bresniker a expliqué que l’on touchait aux limites de la loi de Moore et que les gains de performance des processeurs devenaient de plus en plus marginaux d’une génération à l’autre. Ce ralentissement intervient alors que les quantités de données à gérer explosent.

Amener le "compute" aux données, plutôt que l'inverse

Le but d’HPE avec The Machine est de concevoir un mécanisme qui permette la mise en œuvre d’un vaste pool mutualisé de mémoire entre serveurs et d’amener le « compute » aux données plutôt que l’inverse.

En quelque sorte, nous explique l’un des chercheurs de The Machine, le but est de créer l’équivalent d’un SAN pour la mémoire. A ceci près que ce SAN s’appuiera sur des connexions ultra-performantes et intégrera des mécanismes de sécurisation avancés. HPE parle de « Memory-driven Computing ».

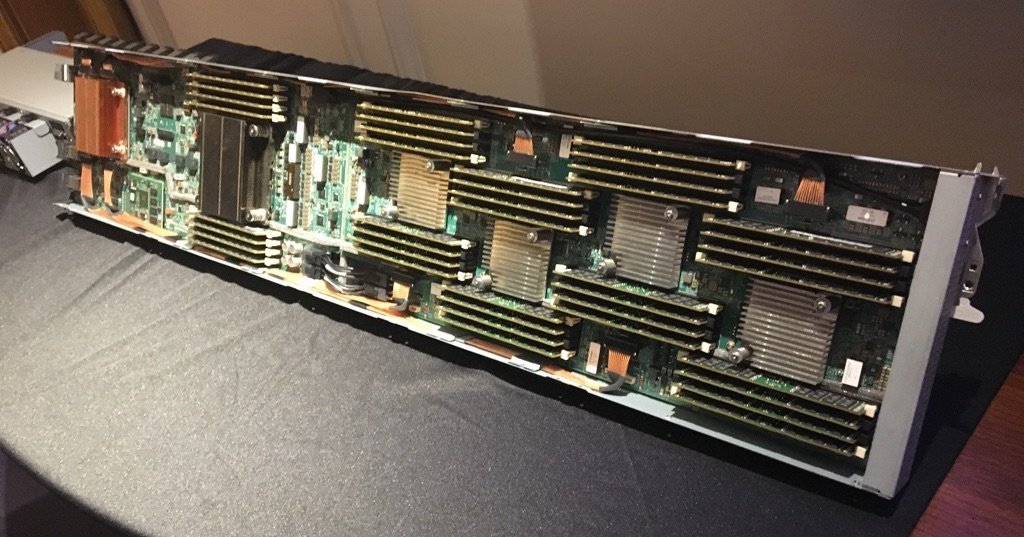

Une lame du prototype "The Machine"

Une lame du prototype "The Machine"

Pour atteindre son objectif HPE a dû résoudre plusieurs problèmes.

Le premier a été de créer une puce qui permet aux serveurs d’accéder à ce vaste pool de mémoire partagée. C’est l’objectif de ce qu’HPE appelle le Next Generation Memory Interconnect, le composant essentiel de la « Memory Fabric ». Il s’agit d’un Asic spécifique au développement duquel ont participé des équipes ayant par le passé travaillé au développement des puces NUMA du constructeur. Il permet à un processeur (ARM, Intel, FPGA ou autres) d’accéder au pool de mémoire partagé de façon transparente.

Le second challenge relevé par la firme a été de créer une architecture d’interconnexion optique à très haut débit pour permettre des échanges de données à des débits compatibles avec les besoins d’une architecture mémoire. Cette architecture d’interconnexion fait usage de composants optiques au silicium (Silicon Photonics). Elle met en œuvre une nouvelle famille de connecteurs permettant le transfert fiable et performant de signaux CWDM (4x25Gbit/s) sur de courtes distances entre serveurs.

The Machine : un premier prototype opérationnel depuis le 24 octobre

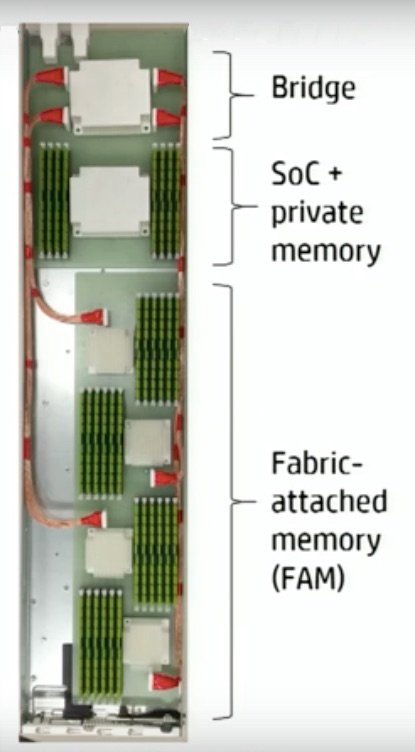

Architecture schématique d'une lame "The Machine"

Architecture schématique d'une lame "The Machine"

Tous ces développements ont été agrégés pour produire un prototype qui a pour la première fois booté avec succès le 24 octobre dernier. Ce système est à base de serveurs lames. Chaque lame serveur se compose de deux parties.

La première est assez traditionnelle puisque l’on trouve un processeur (en l’occurrence un SOC ARM) et sa mémoire DRAM locale. Mais cette portion inclut aussi l’ASIC NGMI d’HPE.

La seconde portion est la mémoire partagée, reliée via de multiples connexions optiques à l’ASIC NGMI. Ce pool peut donc être accédé par le SOC ARM comme s’il s’agissait d’une extension de sa propre mémoire vive interne. Pour l’instant le pool de mémoire est constitué de barrettes de mémoire vive. Mais à terme l’ambition d’HPE est d’utiliser de la mémoire persistante de type ReRam (Resistive RAM) produite en collaboration avec SanDisk, avec lequel HPE a conclu une alliance.

Architecture d'un système multi-lames "The machine"

Architecture d'un système multi-lames "The machine"

Un système The Machine complet se compose de multiples lames en Rack (cf.schéma ci-dessus) et les capacités de mémoire partagée (Fabric Attached Memory) de chaque lame sont agrégées en un pool de plus grande capacité. On peut ensuite interconnecter plusieurs châssis lames, voire plusieurs racks, pour accroître encore la capacité.

Techniquement, le pool de mémoire partagé est adressé sur 75 bits, ce qui ouvre la possibilité de créer un espace mémoire partagé de plusieurs zettaoctets de capacité (rappelons qu’un Xeon E5 adresse sa mémoire sur 46 bits, soit un maximum théorique de 65 Po).

Les défis de la gestion de larges pools de mémoire

La gestion d’un pool de mémoire de cette ampleur pose plusieurs défis.

Le premier est celui de la fiabilité. HPE a conçu plusieurs mécanismes pour s’assurer de la résilience du système, mais aussi gérer et corriger les éventuelles erreurs en lecture/écriture.

Le second défi est celui de la sécurité. Dans The Machine, la sécurité de l’espace mémoire est assurée au niveau matériel. Un serveur ne peut accéder qu’à l’espace qui lui a été autorisé. Si bien que si un OS venait à être compromis sur un serveur, seul l’espace mémoire qui lui est alloué sur The Machine pourrait être compromis.

HPE a aussi mis en œuvre des mécanismes de chiffrement au niveau mémoire. Si quelqu’un volait des composants mémoires dans un système, il ne pourrait accéder aux données stockées. Enfin, HPE prévoit à terme de sécuriser l’architecture de bout en bout, en chiffrant les données avec des clés provisionnées au démarrage (boot) de chaque serveur accédant la mémoire.

Côté performance, les premiers tests menés par HPE avec le prototype ont montré des gains d’un facteur de 15 pour 1 sur des traitements avec Apache Spark, et des gains de 100 pour 1 sur des opérations d’analyse de graphes à très grande échelle.

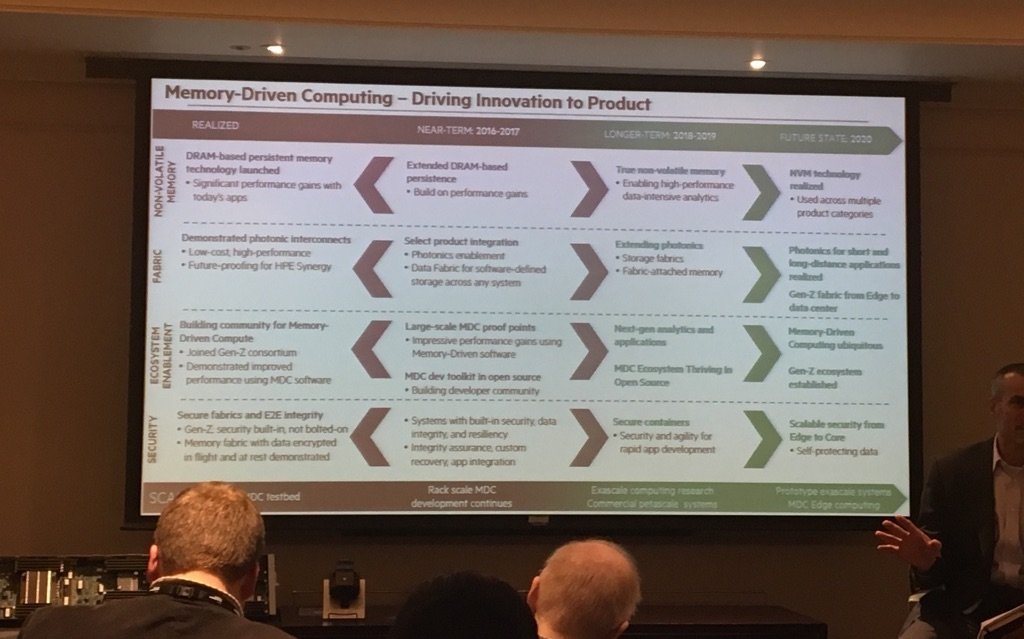

Le calendrier d'évolution vers les architectures mémoire d'HPE

Le calendrier d'évolution vers les architectures mémoire d'HPE

Le démonstrateur actuel n’est toutefois pas conçu pour être commercialisé.

HPE entend poursuivre le développement des technologies de The Machine pour les embarquer progressivement dans ses gammes de serveurs à compter de 2017-2018. Mais ce n’est sans doute qu’après 2020 qu’HPE proposera vraiment des solutions réalisant l’ensemble des promesses de The Machine.