plus69free - Fotolia

A l'OpenPOWER Summit, IBM affiche ses ambitions

Big Blue a profité de l'OpenPOWER Summit, qui se tenait en parallèle de la GPU Technology Conference de NVidia pour lever le voile sur le futur POWER9. Google et RackSpace ont aussi annoncé travailler en commun sur un serveur POWER conforme aux spécifications OCP.

En parallèle de la GPU Technology Conference de Nvidia à San Jose, IBM organisait son OpenPower Summit, une conférence au cours de laquelle Big Blue en a dit un peu plus sur la roadmap Power et sur le développement de l’écosystème autour de l’OpenPower Foundation.

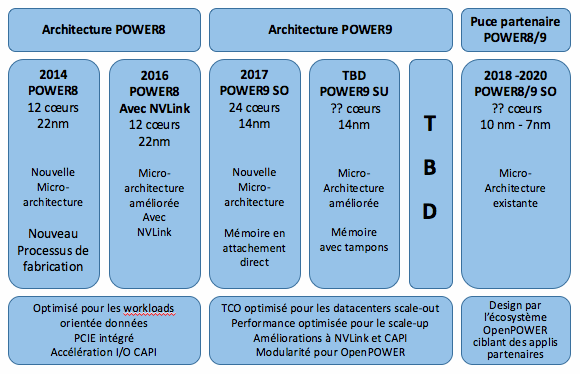

La première nouvelle dévoilée par la firme d’Armonk est la confirmation du lancement au second semestre 2016 d’une version améliorée de l’actuelle Puce Power8 (le supposé Power8+). Cette nouvelle déclinaison de la puce phare d’IBM apportera quelques améliorations en matière de micro-architecture et le support du bus d’interconnexion rapide NVLink de Nvidia qui va permettre à la puce d’échanger des données à très haut débit avec les derniers GPU Tesla P100 à architecture « Pascal ».

Cette intégration de NVLink est un élément clé pour Big Blue. La firme s’est engagée à la fournir pour délivrer plusieurs grands clusters HPC, dont les deux clusters Summit et Sierra du Département de l’énergie US. L’intégration entre les puces Power et les GPU de Nvidia est importante pour Big Blue, qui pense qu’elle sera un différenciateur important afin d’imposer ses puces face à celles d’Intel sur le marché des grands clusters (IBM propose déjà une intégration optimisée avec certains FPGA via son bus propre bus, baptisé CAPI).

Les premiers POWER9 arriveront en 2017

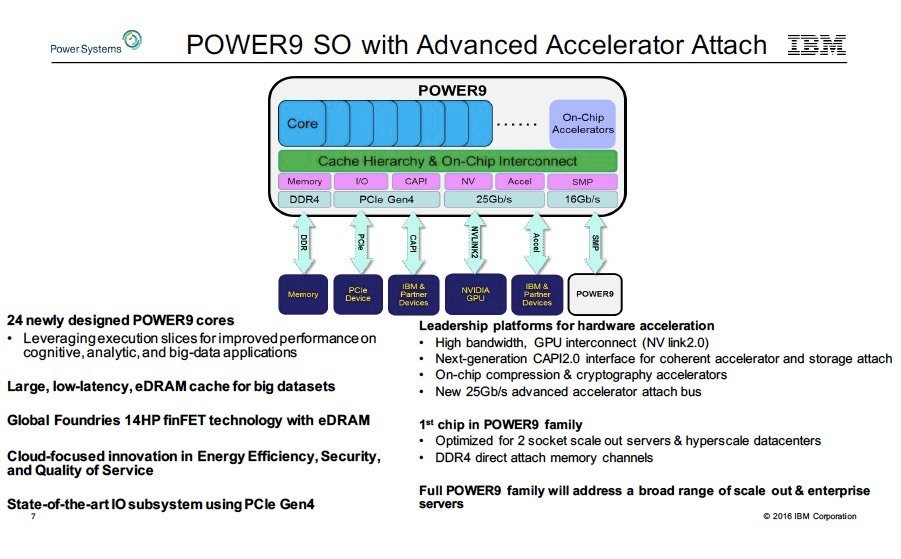

La seconde nouvelle est l’annonce par IBM de son intention de lancer la première de ses puces Power 9 en 2017 (sans doute au second semestre). Le Power9 SO sera fabriqué par Global Foundries en technologie 14nm FinFET. Il disposera de 24 cœurs physiques – Big Blue n’a pas précisé si sa technologie de multhreading SMT sera de la partie pour doper le nombre de cœurs logiques — , supportera en standard la mémoire DDR4 et intégrera des contrôleurs PCIe Gen4. IBM a aussi annoncé que la puce embarquera une version améliorée de NVLink (sans doute la version 2.0 évoquée par Nvidia pour ses futurs GPU « Volta » attendus pour 2018) ainsi qu’une version plus évoluée de l’interface CAPI.

La roadmap POWER selon l'OpenPOWER Foundation

La roadmap POWER selon l'OpenPOWER Foundation

Le suffixe SO derrière Power 9 signifie selon IBM que la puce a été pensée pour des implémentations en mode scale-out .En clair, la puce est optimisée pour être mise en œuvre dans des serveurs bi-socket qui seront directement concurrents de ceux motorisés par les puces Xeon E5 d’Intel.

L'architecture du Power9 SO d'IBM (Source : IBM - Bradley McCredie)

L'architecture du Power9 SO d'IBM (Source : IBM - Bradley McCredie)

IBM n’oublie pas les implémentations Scale-up et proposera sans doute en 2018 une déclinaison SU du Power9 que la firme pourra utiliser dans de futures versions de ses grands serveurs Unix. Entre 2018 et 2020, des entreprises chinoises devraient elles aussi produire une déclinaison de la puce Power9 SO optimisée pour leurs besoins.

Google et RackSpace collaborent sur un serveur POWER9

Une autre annonce intéressante, parmi toutes les annonces matérielles effectuées lors de l’OpenPower Summit 2016 est venue de Google et RackSpace. Les deux sociétés ont annoncé qu’elles collaborent au développement d’un serveur Power9 SO conforme aux spécifications OCP. Baptisé Zaius, le serveur bi-socket 2U imaginé par les deux sociétés disposera de 32 emplacements pour barrettes mémoire DDR4 et de trois emplacements pour cartes PCIe Gen4. Il supportera la technologie NVLink de Nvidia. Cette machine succédera à l’actuel serveur « Barreleye », annoncé au 3e trimestre 2015 et conçu par RackSpace pour fonctionner avec les prochaines puces Power8 et Power8+