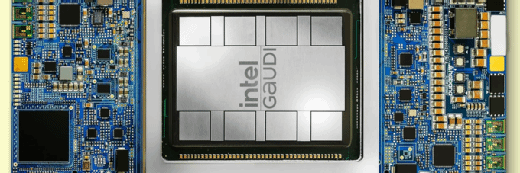

Serveurs : Intel multiplie les GPUs et les processeurs assemblés en « tuiles »

Gaudi2, Greco, Artic Sound-M, Ponte Vecchio, Xeon SPR-HBM... Intel produit plus rapidement ses prochaines puces pour datacenters grâce à un assemblage particulier de circuits gravés indépendamment.

L’époque où Intel n’avait que des processeurs Xeon pour équiper les datacenters est révolue. Le fondeur compte désormais rivaliser avec Nvidia sur les GPUs. Sauf qu’il ne présente pas un modèle d’architecture, mais deux. Le bizarrement nommé Artic Sound-M et son successeur Ponte Vecchio, sont conçus pour générer des images et des univers immersifs côté serveur. Le Gaudi2 et sa déclinaison Greco, eux, serviront pour accélérer les algorithmes d’intelligence artificielle, respectivement le Machine learning (l’entraînement) et l’inférence (le calcul de la décision). Ces puces doivent s’accompagner d’une nouvelle génération de Xeon Sapphire Rapids gravés en 10 nm.

« Notre stratégie est de fournir le plus de solutions possible pour nous adapter exactement aux besoins de nos clients. Nous pensons que l’approche d’avoir un circuit pour tous les usages n’est plus réaliste », a lancé Sandra Rivera, la patronne de la division Datacenter d’Intel, lors de l’événement Intel Vision qui se tenait cette semaine à Dallas et qui marquait le début de la commercialisation de Gaudi 2. Greco et Artic Sound-M seront commercialisés au second semestre. Ponte Vecchio devrait arriver en 2023.

Lors de l’événement Intel Vision, le fabricant de serveurs en marque blanche SuperMicro proposait un premier modèle de machine intégrant le Gaudi2, appelé le X12. La particularité de cette machine est que la carte Gaudi2 n’est plus insérée perpendiculairement dans un slot PCIe, mais clippée horizontalement sur la carte mère. Ce design, issu des travaux du consortium Open Compute, devrait prévaloir aussi pour tous les autres GPU d’Intel.

Une autre caractéristique de tous ces nouveaux GPU est leur conception en « tuiles » (« tiles » en anglais). Afin d’optimiser sa production, Intel maximise la conception à part de chacun de ses circuits et leur assemblage a posteriori. Dans ce processus, les circuits sont individuellement plus simples à graver, donc plus rapides et moins chers à produire.

Cette technique fonctionne, car Intel, notamment avec l’aide du CEA-Leti, dispose de technologies d’assemblage en sandwiches, dites EMIB et Foveros. Elles consistent à relier les pattes de chaque circuit verticalement et horizontalement avec des brins de quelques micromètres à peine. La finesse de ces brins de connexion – 55 micromètres en ce qui concerne EMIB – permet d’éviter les déperditions de vitesse entre les circuits ; ce qui revient pratiquement à des circuits qui auraient été gravés ensemble.

Deux GPU pour l’IA par Habana Labs, partiellement gravés chez TSMC

Gaudi2 et Greco sont issus du laboratoire Habana, une startup qu’Intel a rachetée juste avant la crise pandémique pour deux milliards de dollars. Le mérite d’Habana est d’avoir réussi à vendre ses premières puces – Gaudi et Goya – à AWS, lequel a commencé à les commercialiser dans ses instances DL1 spécialisées en IA en fin d’année dernière.

Lors de l’événement Intel Vision, le laboratoire américain de recherche médicale Leidos témoignait utiliser de telles instances pour entraîner son algorithme d’IA sur la reconnaissance de radios au rayon X. Selon ce retour d’expérience, ces instances seraient 60 % plus rapides – et donc autant moins chères – que les instances d’AWS basées sur des GPU Nvidia, en l’occurrence des V100 d’une génération antérieure.

La particularité de Gaudi2 est que ses 24 cœurs TPC (Tensor Processor Core) côtoient dans la même puce 96 Go de RAM, dite HBM2e (High Bandwidth Memory), car elle est directement interfacée avec le bus des cœurs pour atteindre un débit record de 2,45 To/s. La précédente puce Gaudi disposait de 8 cœurs gravés en 12 nm et d’un débit de 800 Mo/s vers une RAM interne de 32 Go.

Gaudi2 est par ailleurs capable de communiquer avec 24 ports réseau 100 Gbit/s, contre 10 ports réseau sur la précédente génération. Le fabricant de baies de stockage pour supercalculateurs DDN a annoncé lors d’Intel Vision qu’il prend dès à présent en compte cette caractéristique sur sa baie de disques AI400X2.

Au final, Gaudi2 serait 3,2 fois plus rapide que son prédécesseur. En revanche, l’intégration de plus de circuits a un coût : Gaudi2 dissiperait 600 watts de chaleur, soit près de deux fois plus que les 350 watts de son prédécesseur.

Intel insiste surtout sur la comparaison entre Gaudi2 et l’A100 de Nvidia. La nouvelle puce d’Intel serait deux fois plus rapide au test ResNet-50 (qui consiste à reconnaître des images) qu’un A100, que ce dernier intègre 40 ou 80 Go de RAM HBM2e. En face, Nvidia annonce l’arrivée pour la rentrée prochaine d’un H100 qui sera cette fois-ci équipé de 80 Go de RAM HBM3 plus rapide, avec un débit interne prévu aux alentours de 3 To/s.

Un point qui mérite l’attention est que les cœurs d’Habana ne sont pas gravés dans les usines d’Intel, mais dans celles de son concurrent direct, TSMC. Cela est toujours le cas pour Gaudi2 et cela le restera aussi pour Greco, lequel bénéficiera lui aussi d’une nouvelle finesse de gravure en 7 nm. On notera ici l’importance de l’assemblage en tuiles d’Intel : ses propres usines ne permettent pas encore de graver les circuits avec une finesse de 7 nm.

Greco n’intégrera pas de mémoire HBM, mais disposera de 16 Go de RAM LPDDR5 connectés à son bus. Cette mémoire doit lui apporter un débit de 204 Go/s, contre 40 Go/s sur Goya, lequel utilise 16 Go de RAM LPDDR4.

Une famille de GPUs pour des usines à images dans les datacenters

Le futur GPU Artic Sound-M sera autrement plus versatile que Gaudi2 et Greco. Il reposera sur 32 cœurs Xe-HPG, ceux-là mêmes qui composent le GPU Iris intégré aux processeurs Intel Core des PC portables. D’abord destiné aux diffuseurs de média, un seul Artic Sound-M pourra, en même temps, encoder 30 flux vidéo en 1080p ou générer 40 animations temps réel simultanément (Intel parle de serveurs de jeux vidéo en streaming), ou encore diffuser 62 bureaux Windows accélérés en VDI.

Lors de l’événement, Raja Koduri, l’architecte en chef d’Intel, a présenté Endgame, un projet de génération continue d’univers immersif depuis le cloud et qui reposerait sur des serveurs équipés de GPU Artic Sound-M. Sa démonstration consistait à générer les images d’une ville virtuelle très détaillée ; l’animation n’était fluide que lorsque les images étaient précalculées en cloud puis diffusées via une connexion Internet standard vers le PC. Au-delà du jeu vidéo, Intel assure qu’Endgame constitue la base technologique des prochains services de « métavers », des univers immersifs que les entreprises – surtout les banques et les agences de voyages – auraient hâte d’utiliser pour repousser les limites de leur expérience client.

Artic Sound-M est tout autant présenté comme une usine à générer de l’image que comme une puce accélératrice des calculs matriciels. L’élément déroutant est qu’Intel dit qu’il pourra aussi servir à exécuter des algorithmes d’IA, soit comme les GPU des laboratoires Habana.

Ponte Vecchio, le successeur d’Artic Sound-M, intégrera 128 cœurs dans une version améliorée, appelée Xe-HPC. Surtout, il embarquera dans sa puce – comme Gaudi2 – de la RAM HBM, a priori d’une taille comprise entre 16 et 128 Go. Autre nouveauté, un réseau interne appelé Xe Link doit permettre d’enchaîner jusqu’à huit GPUs. Enfin, il disposera de caches à la taille impressionnante : 64 Mo de L1 et 408 Mo de L2. Comparativement, un A100 de Nvidia dispose de 40 Mo de cache L2.

Selon les informations que LeMagIT a pu obtenir, Ponte Vecchio ne sera pas uniquement destiné à être utilisé avec des serveurs Xeon. Les futurs supercalculateurs à base de Rhea, le super processeur ARM de conception européenne, devraient ainsi intégrer des GPU Ponte Vecchio.

Même s’il n’est pas encore officiellement disponible, Ponte Vecchio, alias PVC, est dès à présent dans le supercalculateur Aurora que HPE termine de construire pour le laboratoire de recherche américain Argon National Laboratory. Capable d’atteindre une puissance de 2 Exaflops, cette machine est composée de 10 000 nœuds dont 9 000 sont des serveurs de calcul et le reste des nœuds de stockage. Chacun des nœuds serveur dispose de six GPU Ponte Vecchio équipés de 64 Go de RAM HBM et de deux Xeon Sapphire Rapids spéciaux, eux aussi inédits.

Des Xeon où la RAM est aussi intégrée dans la puce

Les nouveaux Xeon Sapphire Rapids (acronyme SPR) devraient arriver cette année dans les serveurs. Ils reposeront sur les mêmes cœurs Golden Cove que ceux que l’on trouve dans les Core Alder Lake, la dernière génération de processeurs Intel pour PC. Les caractéristiques principales des Alder Lake sont une accélération de 17 % des fils d’instructions et de 60 % sur les algorithmes multithread, le support de la mémoire DDR5 et des bus PCIe 5.0, ainsi que la présence de cœurs « performants » et de cœurs « économiques ». Ces derniers ont un cache et une fréquence moins élevée pour consommer moins d’énergie sur les tâches de fond. Les Xeon SPR auront par ailleurs un circuit d’accélération matricielle AMX qui, lui aussi, doit servir à exécuter des algorithmes d’IA.

Mais le modèle SPR présent dans le super calculateur Aurora a une particularité : comme Gaudi2, comme Ponte Vecchio, il embarque dans sa puce 64 Go de RAM HBM2e. Selon Intel, la présence de cette mémoire HBM au sein même de la puce permettrait au Xeon « SPR-HBM » d’être non plus 60 %, mais 180 % plus rapide que les actuels Xeon Ice-Lake. Selon des benchmarks présentés lors de l’événement, le débit interne de ces Xeon serait de 1,22 To/s.

On ignore à ce stade quelles déclinaisons, de ce processeur SPR-HBM, Intel pourrait proposer dans des serveurs de série ; nombre de cœurs performants ou économiques, quantité de mémoire HBM, fréquences… Mais de telles configurations pourraient être disponibles pour le commun des entreprises d’ici à 2023. Mieux : les cartes mères des prochains serveurs pourront accepter indifféremment des Xeon SPR et des Xeon SPR-HBM.

Les Xeon SPR-HBM présentés lors de l’événement Intel Vision sont constitués de quatre « piles » de circuits, chacune ayant un certain nombre de cœurs (la quantité exacte n’a pas été clairement indiquée) et 16 Go de RAM HBM2e. A priori, ils fonctionnent comme s’il s’agissait d’un cluster de quatre sockets.

Selon Intel, trois fonctionnements sont possibles. Un Xeon SPR-HBM peut considérer que seule sa RAM HBM est la mémoire principale, ce qui permet de fabriquer des serveurs dépourvus de barrettes mémoires. À la manière des tiers de stockage, il peut aussi considérer la RAM HBM comme une zone plus rapide que la RAM DDR externe, afin que le système d’exploitation hôte et les applications choisissent où enregistrer leurs données selon leur importance. Enfin, la mémoire HBM peut simplement servir de cache L4, c’est-à-dire à contenir une copie des données les plus récentes, afin d’accélérer les traitements en cours. Dans le premier et le dernier cas, les applications n’ont pas besoin d’être réécrites pour prendre en compte la mémoire HBM.