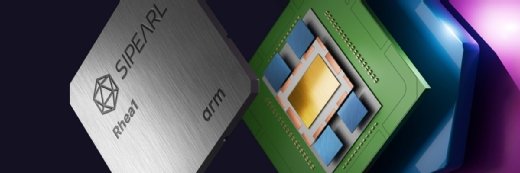

SiPearl : le processeur européen sera un ARM plus puissant qu’un x86

Le Rhea, prévu pour 2022, reposera entre autres sur des cœurs Neoverde Zeus conçus par ARM pour travailler en parallèle – enfin – aussi bien que les puces d’Intel et d’AMD.

Le Rhea de SiPearl, le futur processeur qui garantira l’indépendance de l’UE en matière de supercalcul et d’équipements industriels connectés, sera finalement basé à 80 % sur des cœurs ARM « Zeus ».

« Zeus sera la seconde génération de l’architecture Neoverse, une nouvelle famille de processeurs hautement performants, sur laquelle ARM planche depuis dix ans. Cet accord nous épargne donc dix ans de R&D et va nous permettre de lancer le Rhea dès 2022, comme le prévoit le calendrier du projet européen EPI », explique au MagIT Philippe Notton, le Président fondateur de SiPearl.

SiPearl est l’entité commerciale chargée de concrétiser le processeur qui répond aux caractéristiques de haute performance et de basse consommation imaginées par les 26 membres de l’European Processor Initiative, ou EPI. Ce consortium, sous l’égide de la Commission européenne, a vocation à faire décoller l’activité industrielle de l’UE en apportant à ses acteurs économiques des calculateurs à la fois très performants et non américains.

L’enjeu est de prendre de l’avance sur les recherches en intelligence artificielle, de développer des véhicules autonomes qui seront vendus dans le monde entier ou encore d’automatiser les infrastructures critiques des collectivités locales. L’UE juge primordial que tous ces projets ne soient pas dépendants de composants Intel ou AMD, dont la fourniture pourrait être stoppée par une simple décision politique outre-Atlantique.

Des cœurs ARM, mais aussi Risc-V et Kalray

Avoir fait le choix d’ARM ne met pas totalement le processeur européen à l’abri des risques géopolitiques. Initialement britannique, ARM est passé sous pavillon japonais en 2016, suite à son rachat par SoftBank Group, un géant des télécommunications. D’ailleurs, les membres de l’EPI auraient des discussions passionnées à propos d’une alternative plus neutre : les processeurs Open source Risc-V (prononcer « Risc 5 »). Née dans les universités de la Silicon Valley, l’architecture Risc-V se trouvait d’abord sous la tutelle d’une fondation américaine. Celle-ci a décidé en 2019 de se placer sous juridiction suisse, justement pour ne pas courir de risques de blocus.

« Les processeurs Risc-V sont encore très jeunes et tout reste à inventer. En prenant le parti de construire notre processeur sur un jeu d’instruction ARM, nous nous donnons l’avantage d’un écosystème : notre processeur bénéficie d’ores et déjà de compilateurs pour écrire ses applications et de systèmes Linux pour les exécuter », rétorque Philippe Notton. Et de préciser que si l’EPI donne les objectifs, SiPearl a carte blanche pour les atteindre.

Les risques d’un blocus sont de toute manière à relativiser : contrairement à Intel et AMD, ARM ne vend pas de processeurs. Il se contente d’en faire le design. De plus, concernant la nouvelle architecture Neoverse, les ingénieurs d’ARM sont désormais basés en France, à Sophia Antipolis.

« Cela dit, les cœurs ARM ne représenteront que 80 % de notre processeur Rhea. Ils exécuteront les codes applicatifs et il y en aura d’autres pour les fonctions d’infrastructure. Nous intégrerons donc bien des cœurs Risc-V pour gérer la sécurité, mais aussi des cœurs Coolidge du Français Kalray, pour répartir les calculs afin qu’ils s’exécutent en un nombre donné de cycles. Ces fonctions-là ne seront utilisées que par notre firmware. Dans ce cas, l’inexistence d’un écosystème pour les développeurs tiers n’a pas d’importance », ajoute-t-il.

Reste la fabrication même des processeurs. SiPearl prévoit de passer par les usines du Taiwanais TSMC. Mais puisque même les Américains Intel et AMD utilisent désormais les chaînes de production asiatiques, il est peu probable que cette situation favorise la souveraineté des uns au détriment des autres.

L’enjeu de réellement rivaliser avec les x86

Tout l’enjeu de l’architecture Neoverse est d’implémenter les circuits qui rendent les processeurs x86 plus efficaces quand il s’agit d’exécuter plusieurs applications en même temps. Malgré tous les efforts d’ARM pour créer depuis des décennies des processeurs très rapides et très peu énergivores, les différentes implémentations, que ce soit chez Apple, chez Samsung, ou chez Qualcomm, ne fonctionnent en pratique que sur des appareils où une seule application à la fois est utilisée, en plein écran.

Ce défaut n’a pas empêché ARM d’être aujourd’hui la technologie omnipotente sur smartphones, tablettes et autres équipements grand public. Il est en revanche rédhibitoire pour la carrière de ses processeurs sur PC et serveurs. Les ventes de PC portables ARM, principalement des machines Windows 10 basées sur le Snapdragon de Qualcomm, ne décollent pas. En cause, la logithèque peu fournie : les développeurs ne parviennent pas à adapter simplement sur ARM leurs logiciels x86 multifenêtrés. Un émulateur x86 est fourni sur ces machines, mais il n’est pas capable d’exécuter les codes 64 bits, désormais majoritaires.

Côté datacenters, HPE se serait cassé les dents à essayer de vendre aux entreprises des serveurs VDI à base d’ARM, les Proliant m400 et m800. Selon nos sources, cette solution, où chaque poste distant avait droit à son serveur physique dédié, était moins performante et pas vraiment moins énergivore qu’une solution traditionnelle à base de postes virtualisés depuis des machines x86. En fin de compte, seuls les acteurs du cloud public semblent ici tirer profit d’une architecture ARM pour motoriser des sites web simples, c’est-à-dire monotâches.

Passer les ARM en 64 bits et y multiplier les cœurs ne change rien au problème, qui repose sur un détail technique plus subtil. Les x86 d’Intel et AMD sont capables d’exécuter les instructions dans le désordre et, mieux, de prédire vers quel endroit d’un code il faudra bientôt sauter. Leur mémoire cache en devient plus efficace : elle contient plus souvent les informations utiles et distribue mieux les instructions aux différents cœurs. Les cycles d’exécution sont plus souvent occupés sur x86, tandis que les ARM perdent sempiternellement du temps à repartir chercher leurs données dans des zones plus lentes de la mémoire.

Ce type d’exécution, dit Out-of-Order, existe dans les processeurs ARM actuels, mais à un stade précaire. Il repose sur une modification à la volée des adresses en mémoire, ce qui pose un tel risque d’erreurs que son usage est restreint. En pratique, sur ARM, les cœurs multiples et le cache ne sont exploités que par une application à la fois. Et encore, uniquement si celle-ci a été programmée pour en tirer parti.

En améliorant l’exécution Out-of-Order et la prédiction de saut sur les processeurs Neoverse, ARM se donne donc les moyens de jouer à armes égales contre Intel et AMD quel que soit l’usage de la machine hôte. Ses cœurs deviennent dès lors autant efficaces que ceux des Intel Core/Xeon ou AMD Ryzen/Epyc pour exécuter simultanément des flux qui traitent des données différentes, comme c’est particulièrement le cas en supercalcul et dans les moteurs de Machine Learning. Conjuguée à la faible consommation historique des puces ARM, cette nouvelle capacité devrait même permettre aux processeurs de la famille Neoverse d’être plus efficaces en termes de Gflops/watts que les x86.

Standardiser les efforts de Cavium sur le ThunderX2

Avec l’architecture Neoverse, ARM ne fait que standardiser des techniques qui ont été précédemment expérimentées par Cavium sur son ThunderX2, un ARM qui équipe déjà le supercalculateur BullSequana qu’Atos a commencé à livrer au CEA dès la fin de l’année 2018. Selon Philippe Notton, le projet EPI est d’ailleurs la suite logique du projet européen MontBlanc qui visait, dès 2017, à construire des supercalculateurs européens à base de processeurs Cavium pour créer un écosystème ARM dans le domaine et, à terme, parvenir à se passer de puces américaines. Les apports du ThunderX2 sont tels, que Cavium a entretemps été racheté par l’Américain Marvell. Il a même incité HPE à se relancer dans le développement de serveurs ARM.

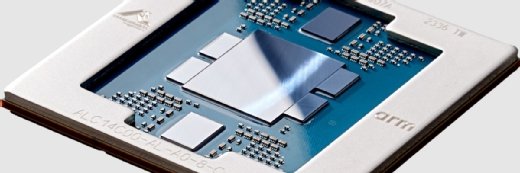

L’architecture Neoverse a déjà connu une première implémentation, celles des cœurs Ares, alias N1. Lancés en 2019, les cœurs ARM N1 ont été intégrés tout récemment par l’Américain Ampere Computing dans son processeur Ampere Altra, de 80 cœurs. Tout comme le Rhea, l’Ampere Altra se destine d’abord aux supercalculateurs et, dans un second temps, aux équipements embarqués. Gravé en 7 nm, il fonctionne à plus ou moins 3 GHz, mais ne consomme que 210W. Fondé par des anciens d’Intel avec l’objectif de faire de l’ARM le nouveau Xeon, Ampere s’est bâti sur le rachat en 2018 des travaux d’Applied Micro en matière de processeurs ARM 64 bits. Sa première puce ARM, l’eMag, aurait été achetée en 2019 par Lenovo dans le but de construire des serveurs pour les hébergeurs web.

Zeus, la seconde génération de cœurs Neoverse, ne sera dévoilé que d’ici à la fin de l’année par ARM ; on ignore encore ses améliorations par rapport à Ares/N1. En attendant, SiPearl ne souhaite pas non plus communiquer les détails du Rhea. Tout au plus, sait-on que SiPearl a pris une licence de la version POP de Zeus, celle qui fonctionne avec des transistors de type FinTET, le format requis par TSMC pour ses chaînes de gravure en 6 nm.

Les cœurs Zeus devraient également servir à bâtir des processeurs chez Fujitsu et Huawei, les puissances asiatiques ayant les mêmes désirs d’Indépendance technologique que l’Europe. Marvell a lui aussi annoncé qu’il planche sur une implémentation de Zeus.

En 2024, le Rhea sera décliné dans une version moins fournie en cœurs, pour adresser le secteur de l’IoT. Selon les feuilles de route des industriels de l’automobile, il serait embarqué dans des équipements urbains disposés le long des voies, plutôt qu’à bord des véhicules. A priori, cette seconde version du Rhea sera basée sur le successeur de Zeus, c’est-à-dire sur la troisième génération de l’architecture Neoverse.