Cavium dévoile ses puces ARM 64bit serveur à 48 coeurs

Cavium a profité du salon Computex de Taipei pour lever le voile sur sa famille de processeurs ARMv8 ThunderX, des puces ARM 64bit serveurs à 48 coeurs cadencés à 2,5 GHz.

Petit à petit l’architecture ARM 64-bit se concrétise. Si Apple a été le premier à proposer des puces 64-bit ARM dans ses tablettes et téléphones mobiles, le véritable enjeu de l’émergence de l’architecture ARM v8 est d’apporter une concurrence aux puces x86 64-bit sur le marché des serveurs. Et le moins que l’on puisse dire est que Cavium vient de frapper fort en profitant du selon Computex qui se tenait à Taïwan, pour dévoiler ses puces Thunder X, des puces clairement destinées au marché des serveurs et des datacenters.

Les Cavium ThunderX sont des processeurs ARM basés sur l’architecture ARM v8 et donc l’architecture est le fruit des travaux de la firme. En ce sens, Cavium ne s’est pas contenté, comme AMD, de s’appuyer sur les designs d’ARM, mais a développé sa propre architecture de cœurs ARMv8.

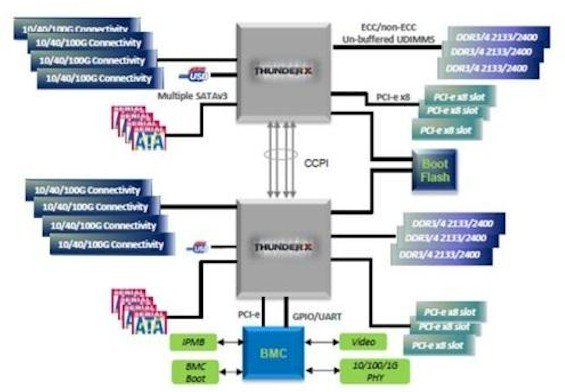

Chaque puce ThunderX embarque 24 ou 48 cœurs cadencés jusqu’à 2,5 GHz et gravés en 28nm. Le tout est épaulé par un vaste ensemble de coprocesseurs pour la gestion du réseau, l’accélération du chiffrement ou l’accélération de fonctions réseau (analyse de paquet profonde, filtrage, trafic shapping, antivirus et antimalware…). Les SOC de Cavium embarquent aussi leurs propres contrôleurs PCI-express 3.0, leurs propres contrôleurs mémoire DDR3 et 4 ainsi qu’une technologie d’interconnexion rapide, permettant l’agrégation de plusieurs processeurs sur une même carte mère.

Selon Cavium, son architecture est 100 % compatible avec la spécification SBSA (Server Base System Architecture), une spécification conçue par ARM et ses partenaires (AMD, Broadcom, Canonical, Cavium, Citrix, Dell, HP, Red Hat, Suse, TI) pour standardiser l’écosystème serveur ARM et assurer un fonctionnement transparent des principaux OS sur les différents processeurs ARM destinés au marché des serveurs. Chaque SOC Cavium ThunderX inclut jusqu’à 48 cœurs épaulés par 16 Mo de cache de niveau 2 et intègre un bus d’interconnexion (CCPI ou Cavium Coherent Processor Interconnect) supportant la cohérence de cache pour permettre l’agrégation sur une même carte mère de jusqu’à deux processeurs. Chaque puce embarque également un contrôleur réseau avancé fournissant de multiples interfaces 10Gigabit et 40 Gigabit Ethernet ainsi que son propre contrôleur PCIe et ses propres contrôleurs mémoire. L’ensemble de la puce supporte la virtualisation via la technologie virtSOC, ce qui veut dire que l’IOMMU intégré pourra être piloté par les hyperviseurs intégrés aux OS comme KVM ou Xen.

Les puces seront proposées dans différentes versions supportant des accélérateurs spécifiques pour certaines fonctions de stockage et de réseau, comme le support du protocole RoCE (RDMA over Converged Ethernet) le support des technologies NITROX et TurboDPI de Cavium pour l’accélération IPSec et SSL, et l’accélération des services anti-virus, anti-malware, ou la fourniture de services avancés de pare-feu et de filtrage de paquets. L’objectif est par exemple de fournir des fonctions à même de servir dans des appliances serveurs web ou dans des appliances de sécurité.

Cavium indique avoir travaillé en amont avec les acteurs du logiciel pour assurer le support de ses puces par les grandes distributions Linux et par les hyperviseurs libres tels que Xen ou KVM. La firme annonce aussi un support complet par la chaîne d’outils de compilation GCC et un support complet de Java. Rappelons pour mémoire que Cavium dispose non seulement d’expertises matérielles, mais aussi d’expertises logicielles, via son rachat en 2009 de Montavista, l’un des grands développeurs de technologies Linux embarquées. Montavista a notamment travaillé sur des versions optimisées de KVM pour les applications temps réel et a également beaucoup travaillé sur les questions de virtualisation de fonctions réseau (NFV) et de SDN. Autant de compétences qui pourraient s’avérer précieuses pour les applications visées par les dernières puces annonces par le constructeur.

Selon Cavium, ses puces seront disponibles pour évaluation au tout début du 4e trimestre ; ce qui veut sans doute dire que l’on pourrait voir les premiers serveurs embarquant les puces de Cavium dans le courant du premier trimestre 2015. HP, notamment, travaille avec Cavium pour développer une cartouche ARM 64-bit pour sa ligne de serveurs Moonshot.