AMD apporte la virtualisation d'entrées/sorties à ses prochaines plates-formes serveurs

Ce n'est finalement pas un chipset qu'AMD a annoncé cette semaine, mais trois, tous conçus pour supporter tant les actuels Opteron "Istanbul" que les futures puces à 12 cœurs et 6 cœurs attendues au premier trimestre 2010 avec la plate-forme "Maranello". Offrant des performances en hausse et le support de la virtualisation d'entrées/sorties, ces composants ont été immédiatement adoptés par les intégrateurs taïwanais, mais ne devraient logiquement apparaître chez les grands constructeurs qu'au premier trimestre, lors de la refonte de l'offre de processeurs pour serveurs d'AMD.

Alors qu'il ne devait, à l'origine, lancer qu'un seul chipset à la rentrée dans le cadre de sa plate-forme Fiorano, AMD a dévoilé cette semaine pas moins de trois jeux de composants différents conçus pour motoriser la prochaine génération de ses serveurs Opteron.

Ce printemps, AMD avait annoncé l'arrivée pour la rentrée de sa plate-forme Fiorano, combinant les puces Opteron "Istanbul" avec l'I/O Hub SR5690 et un SouthBridge baptisé SP5100. Objectif : remettre à niveau les plates-formes serveurs d'AMD par rapport à celles d'Intel avec notamment le support de la virtualisation d'entrées/sorties. Pour cela, AMD a intégré au SR5690 une unité de gestion IOMMU (I/O Memory Management Unit), une technologie qu'Intel avait déjà insérée dans ses plates-formes serveurs à l'occasion du lancement des Xeon 5500 et des chipsets associés (Intel 5500 et Intel 5520). Les capacités de virtualisation d'entrées/sorties d'AMD héritent de l'appellation marketing AMD Vi alors qu'Intel a regroupé les siennes sous la dénomination VT-d.

[lire notre enquête : AMD, en quête de rachat après la débâcle de Barcelona]

Mais, finalement, l'I/O Hub SR5690 n'arrive pas seul. Le SR5670, prévu à l'origine pour le premier trimestre 2010 dans le cadre de la plate-forme Maranello (bi et quadri-socket à base de processeur Opteron 6000, le 12 coeurs "Magny-Cours", et la puce à six coeurs "San Paulo"), est lui aussi disponible. De même, AMD a avancé la sortie du SR5650, certainement programmée à l'origine pour l'arrivée de la plate-forme "San Marino" à base d'Opteron 4000 (Opteron hexa-coeurs "Lisbon").

Des performances accrues et une consommation maîtrisée

Tous ces I/O Hub apportent le support de l'IOMMU et sont donc bien adaptés à un usage en environnement virtualisé. Ce qui les distinguent essentiellement réside dans le nombre de lignes PCI-express 2.0 gérées. A la clef une aptitude à encaisser un nombre plus ou moins élevé d'entrées/sorties. Le SR5690 dispose ainsi de 11 moteurs PCI-express et peut gérer 42 voies PCI-express (avec support de l'insertion à chaud), tandis que le SR5670 ne dispose que de 9 moteurs pour 30 voies PCI-express. Le 5650 intègre enfin 8 moteurs pour 22 voies PCI express 2.0.

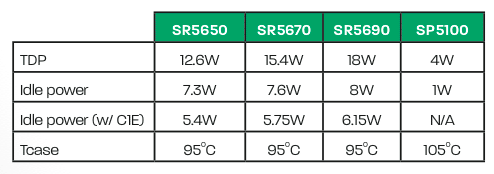

Bien sûr, ces chiffres se traduisent par une consommation énergétique plus ou moins élevée. Ainsi le SR5690, qui vise plutôt le marché des serveurs quadri-socket et au-delà, a la consommation la plus élevée avec une dissipation thermique typique de 18 W (8 W au repos). Le SR5670, conçu pour les serveurs bi-socket ayant besoin de bonnes capacités d'I/O, affiche quant à lui une enveloppe thermique (TDP) de 15,4 W (7,6 W au repos), tandis que le SR5650, destiné aux serveurs à basse consommation, affiche un TDP de 12,6 W et une consommation au repos de 7,3 W. A titre de comparaison les I/O Hub Intel 5500 et 5520 que le fondeur fournit avec ses Xeon 5500 ont un TDP de 27,1 W pour un nombre de lignes PCI-express respectif de 24 et 36.

La fournée de composants AMD travaille de concert avec le nouveau SouthBridge d'AMD, le SP5100, qui fournit la connectivité USB (12 x USB 2.0), les ports SATA (3GBit/s) et les ponts vers les vieux bus PCI. La connexion entre les différents composants du chipset étant assurée par le bus Hypertransport 3.0.

Une généralisation au premier trimestre 2010

Ces nouveaux chipsets sont compatibles avec les puces Istanbul actuelles et leur Socket F. Ils sont aussi conçus pour supporter les futurs sockets AMD, le G34 (Maranello) et le C32 ("San Marino"). En toute logique, on ne devrait les voir apparaître dans des serveurs de grands constructeurs qu'au premier trimestre 2010, lors du lancement de la plate-forme Maranello et des processeurs "Magny-Cours" et "San Paulo".

Il est en effet peu probable qu'un grand constructeur mette à jour ses cartes mères pour supporter le vieux socket F alors que ce dernier sera obsolète d'ici l'été 2010. Sun, qui à l'origine avait été tenté d'utiliser les nouveaux chipsets dans certains de ses serveurs, y a vraisemblablement renoncé. La voie est donc libre pour les habituels intégrateurs taïwanais, comme Tyan ou Supermicro, qui ont tous annoncé des designs à base des nouveaux chipsets. L'un des marchés ciblés est sans surprise celui du HPC (calcul hautes performances), pour lequel l'accroissement des bandes passantes offertes par les nouveaux chipsets constitue un vrai plus...

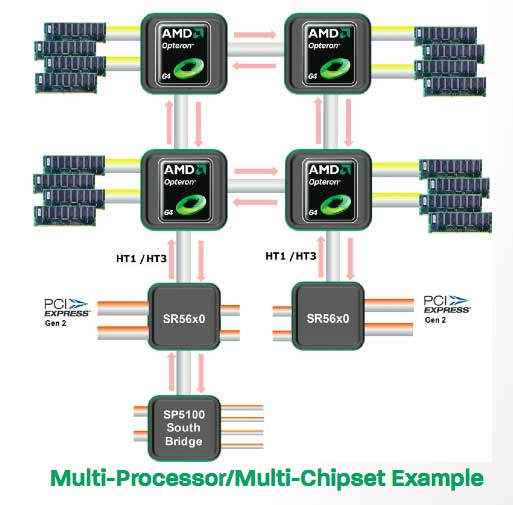

Notons pour terminer qu'AMD prévoit que certains constructeurs intégreront deux I/O Hub sur leurs plates-formes les plus performantes, une façon d'assurer une certaine redondance, mais aussi d'obtenir des entrées/sorties beaucoup plus équilibrées sur les futures plates-formes quadri-socket à base de puces à 12 coeurs « Magny-Cours ».