AMD en quête de rachat après la débâcle de Barcelona

Après avoir enfin sorti ses puces Opteron quadri-coeur "Barcelona" avec plus d'un an de retard, AMD vient de refondre sa feuille de route pour ses futurs processeurs. Objectif : rassurer clients et partenaires avec un calendrier tenable tant du point de vue technologique que d'un point de vue délais. Car si AMD peine, Intel a, de son côté, tiré un trait sur les problèmes du milieu des années 2000. Et sa feuille de route n'entend laisser aucun répit à son rival.

Alors que la plupart des constructeurs viennent de mettre à jour leurs serveurs Opteron pour accueillir la dernière génération de puces quadri-coeurs d'AMD, l'Opteron « Barcelona », LeMagIT revient sur les calendriers de production des processeurs d'Intel et d'AMD. Ce dernier a refondu son calendrier de sortie de processeur (on parle de roadmap) à la mi-mai afin de rassurer les utilisateurs après la débâcle du lancement de « Barcelona ».

Comme Intel en 2005/2006, AMD se retrouve contraint de revoir ses plans pour retrouver une offre technique crédible face à son concurrent. Reste à savoir si cette opération connaîtra le même succès que celle qu'a menée Intel il y a quelques années...

La débâcle du quadri-coeur

Pêché de gourmandise ? Toujours est-il que les plans (trop ?) ambitieux d'AMD pour ses puces Opteron quadri-coeur se sont retournés contre le fondeur au pire moment, alors qu'il avait l'oreille des entreprises et la confiance des constructeurs de serveurs. En moins d'un an, ce capital confiance s'est volatilisé, et AMD se retrouve dans la situation où il était il y a cinq ans, c'est-à-dire à devoir convaincre partenaires et clients de la pertinence de ses solutions.

Le quadri-coeur « Barcelona », c'est l'histoire d'une crise d'Hubris d'AMD, la volonté de montrer qu'il pouvait faire bien mieux qu'Intel en produisant un vrai quadri-coeur au lieu de se contenter comme son concurrent d'assembler deux puces bi-coeurs pour en faire un quadri-coeur. Le challenge était de taille et s'est avéré bien plus compliqué que prévu. De dérapage en dérapage, de report en report, Barcelona est devenu l'arlésienne d'AMD. Et lorsqu'avec près de 18 mois de retard sur Intel, AMD a officiellement lancé son « vrai » quadri-coeur, cela n' a été que pour mieux le retirer. Un bogue critique venait en effet d'être détecté dans le TLB (Translation lookaside buffer), une portion du cache CPU utilisée par le processeur pour effectuer les translations d'adresse mémoire entre mémoire physique et adresses virtuelles. C'est donc penaud, avec 24 mois de retard sur les premiers quadri-coeurs d'Intel, qu'AMD a enfin lancé Barcelona. La puce qui devait assoir définitivement sa réputation sur le marché des serveurs venait en quelques mois de la ruiner.

Intel a repris l'avantage technique

Le drame pour le fondeur texan est que Barcelona est une excellente puce, mais que pour avoir l'avantage sur les Xeon d'Intel, elle aurait du sortir à l'automne dernier. Entretemps, le numéro un mondial a encore progressé et il a désormais l'avantage technique dans la plupart des compartiments du marché, à l'exception du très haut de gamme et notamment des serveurs quadri-socket et octo-socket, où l'architecture NUMA du bus de l'Opteron reste encore supérieure à celle du bus partagé des Xeon MP. Ce qui vaut à AMD de contrôler plus de 50% de ce marché.

AMD et Intel : histoires de coeurs...

Il y a quinze jours, AMD a annoncé une refonte massive de son calendrier processeur afin d'offrir une parade plus efficace aux puces d'Intel. La première victime de cette refonte est la famille de puces octo-coeur SandTiger qui était attendue pour la fin 2009. Sandtiger, un « vrai » octo-coeur, devait utiliser un nouveau support (ou socket) processeur, le socket G, et apporter plusieurs améliorations essentielles dont l'inclusion de quatres liens Hypertransport 3.0, la gravure en 45 nm et un nouveau coeur CPU baptisé Bulldozer. Ces améliorations seront graduellement embarquées par les nouvelles familles de puces annoncées par AMD en remplacement. Ces dernières s'appuieront sur une architecture hexa-coeur conçue pour permettre à AMD de contrer les futures puces hexa-coeur Dunnington d'Intel.

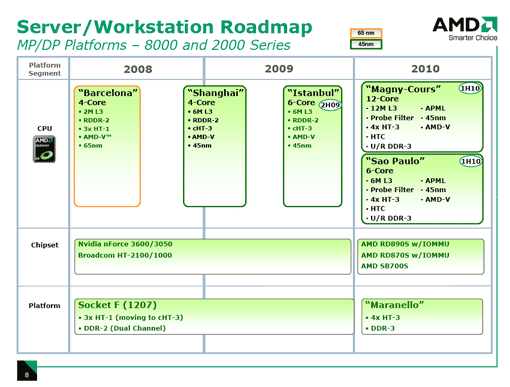

La nouvelle roadmap d'AMD (Source : AMD)

Dans l'immédiat la priorité d'AMD est de rattraper Intel sur le 45 nm afin de rester compétitif sur le marché des serveurs bi-socket, qui représente la plupart des ventes de serveurs x64 en volume. Pour cela, AMD devrait lancer un successeur à « Barcelona » gravé en 45 nm dès la fin de l'année 2008. Connue sous le nom de code « Shangai », la nouvelle puce utilisera le socket F d'AMD, ce qui lui permettra d'être déployée sur l'ensemble des serveurs conçus pour Barcelona. Shangai devrait embarquer 6 Mo de cache de niveau 3, soit trois fois plus que Barcelona. La puce pourra aussi compter sur ses trois liens cohérents Hypertransport 3.0 pour doper les entrées-sorties (à comparer aux aux trois liens Hypertransport 1.0 de « Barcelona »). AMD estime qu'à fréquence équivalente, Shangai offrira des performances 20 % supérieures à celles de Barcelona, tout en abaissant la consommation électrique.

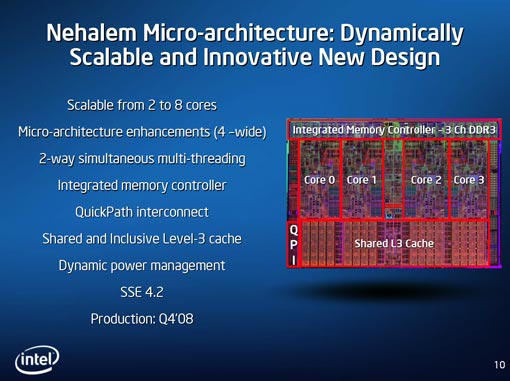

QPI : un nouveau bus point à point Intel face à Hypertransport

Dès le premier trimestre 2009, Shangai devra affronter le Xeon Gainestown, le premier vrai quadri-coeur d'Intel, une puce basée sur la nouvelle architecture Nehalem et sur son bus d'interconnexion point à point QPI (QuickPath Interconnect). QPI est la riposte d'Intel à Hypertransport et il devrait permettre de doper significativement les débits mémoire du bus des Xeon (Intel annonce un triplement de la bande passante entre GainesTown et l'actuel Xeon 5400 « Harpertown »), faisant disparaître l'un des grands avantages des puces Opteron sur leurs concurrentes. Il est vraisemblable que la puce d'Intel aura l'avantage en matière de performances sur celle d'AMD, à moins que le Texan ne parvienne à pousser la fréquence d'horloge de Shangai.

L'architecture de Gainestown, la première puce Nehalem (Source : Intel)

Shangai aura aussi la difficile mission, sur le marché des grands serveurs x86, de faire face à Dunnington, une puce hexa-coeur massive dont Intel à le secret. Dotée de 16 Mo de mémoire cache de niveau 3, ce composant sera la dernière des puces Intel basée sur le coeur « Penryn ». Sa seule raison d'être sera de tenter de casser la domination d'AMD sur le marché des grands serveurs, un marché qui connait un regain d'intérêt de la part des entreprises pour les architectures de datacenters virtualisés. Comme ses prédécesseurs, Dunnington devrait toutefois pêcher du côté des entrées-sorties, puisque la puce utilisera le bus système partagé moribond cher à Intel.

Pour riposter à Dunnington et Gainestown, AMD a toutefois un as dans sa manche. En torpillant l'octo-coeur Sandtiger, AMD a en effet fait la place à une puce à six coeurs attendue pour la seconde moitié de 2009. « Istanbul » embarquera six coeurs gravés en 45 nm et sera elle aussi compatible avec les cartes mères conçues pour « Barcelona ». Ce composant devrait permettre à AMD de reprendre l'avantage en matière de performance tant sur le marché des serveurs bi-socket, que sur celui des grands serveurs.

2010 : 32 nm chez Intel contre 12 coeurs chez AMD

A compter du début 2010, la bataille de l'hexa-coeur devrait faire rage puisque Intel entend introduire un composant de ce type pour serveurs bi-socket au premier trimestre. Baptisé Westmere, ce processeur sera le premier de la firme gravé en 32 nm. Il sera accompagné d'un octo-coeurs pour grands serveurs x64, le Xeon MP « Beckton », un monstre doté de 24 Mo de mémoire cache et, pour la première fois sur ce segment de marché, de quatre bus QPI.

Pour contrer Intel, AMD profitera de 2010 pour introduire un nouveau socket processeur, le socket G34, et deux nouvelles puces gravées en 45 nm. Attendu pour le premier semestre 2010, San Paolo sera doté de 6 coeurs légèrement revus par rapport à ceux d'Istanbul et de 12 Mo de cache de niveau 3. il embarquera aussi 4 liens Hypertransport 3 et le support de la mémoire DDR3. En milieu d'année, San Paolo sera rejoint par « Magny Cours », une puce dotée de 12 coeurs processeurs. Pour cette dernière, AMD emploiera une recette éprouvée par HP avec l'Itanium ou par Intel avec ses Xeon, à savoir le packaging en une seule puce de deux processeur San Paolo. Pour avoir une idée de la progression technologique attendue par AMD, une puce Magny Cours devrait consommer l'équivalent de l'actuel « Barcelona ».

La virtualisation des entrées-sorties

Il est à noter que les puces San Paolo et Magny Cours utiliseront une plate-forme serveur baptisée "Maranello". Les chipsets conçus pour cette plate-forme supporteront la virtualisation d'entrées-sorties, grâce à l'inclusion de ce qu'AMD appelle l'IOMMU (I/O Memory Management Unit). L'IOMMU d'AMD devrait fournir des services similaires à VT for Directed I/O d'Intel et permettre aux grand hyperviseurs de virtualiser aussi les entrées-sorties (Ethernet, Infiniband, Fibre Channel...) en plus des ressources mémoire et processeur. Seul souci, l'ajout de l'IOMMU était à l'origine prévu pour SandTiger en 2009. Il aura donc près d'un an de retard sur la roadmap initiale d'AMD.

Course à la puissance : une bataille futile ?

On le voit : AMD et Intel devraient se rendre coup pour coup au cours des deux prochaines années. Reste que la bataille pour les performances n'est plus aussi importante qu'autrefois. La plupart des serveurs x86 modernes en production dans les entreprises sont utilisés entre 10 et 15% de leurs capacités. La bataille sur le seul critère absolu des performances du processeur est donc absurde, sauf pour les applications de calcul et le HPC (High Performance Computing), où chaque cycle d'horloge compte.

Même en environnement virtualisé, l'objectif n'est pas d'atteindre 100% de la capacité du serveur mais plutôt un sage 40 à 50%, déjà bien supérieur au taux d'utilisation actuel. Résultat, le coût de la plate-forme, sa stabilité dans le temps, son aptitude à la vitualisation, sa consommation électrique deviennent des critères de choix bien plus pertinents.

Et en la matière, bien malin sera celui qui pourra faire la différence entre les différentes offres des deux fondeurs.